CDプレーヤー(CDP)の歴史はもう長い、30年近くなる。なので相当進化したはずだ・・・と思ったら大間違いで、いまだ16ビットの淵をさまよっているというか、ひどい事になっているような気がする。

そんな事はない、ハイエンドのDACチップはダイナミックレンジが120dB以上あるし、最近は32ビットのDACチップもでてきた、FIFOでジッターを減らす技術も取り入れられているものもあるし、マスタークロックを入れればもっと良くなるetc.。

でも調べてみるとCDPの動作は目も当てられない状態になっているというしかない。調べているこちらの装置の状態がおかしいのじゃないかとまず疑わなければいけないくらいだ。一番すごい事になっているのはDAC以降の回路動作だが、そこはまだおしゃべりできないので、今回はデジタル回路の部分について紹介する。

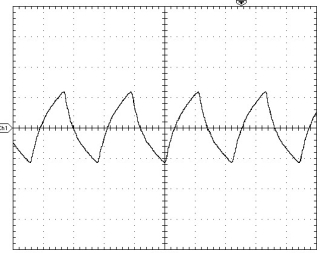

ここで問題です。

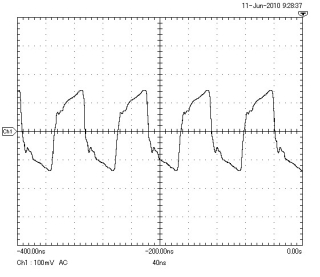

これは何の波形でしょうか?

ここでご愛読のお礼におまけを一つ、

ずばり当たった方は弊社製品購入の機会がありましたら2割引きします。–>締め切りました。

(ただし最大割引料金3万円まで、2割引の有効期限1年間、コメント欄に正解を記入していただいた方に限ります。先着3名様まで、次回執筆時までの期限限定で)—>締め切りました。

注:コメント欄に個人情報は書かないで下さい。

答えは次回執筆時に。答えはマスタークロックです。出題後、1時間もしないうちに正解の回答をいただき正直面食らいました。

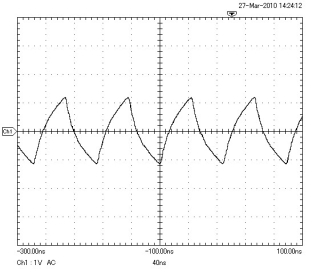

同じ波形を時間軸も入れて見せるとこうなります。

マスタークロックの波形11.3MHz, 40ns/div

マスタークロックの波形11.3MHz, 40ns/div

CDのサンプリング周波数(Fs)は44.1Khzですが、CDPのデジタル出力をDACに入れると専用に設計されたレシーバーICがこのFsの256倍の11.2896MHzのマスタークロックを作ってくれて、DACチップに渡すようになっています。本来マスタークロックは矩形波のはずですが、実際にはこんなに鈍っていた。11MHzの矩形波を綺麗に伝送するには最低でも5倍できれば10倍以上の帯域が必要で50-100MHzの帯域がないと矩形波にならない。なので結構難しい事なのかも知れない。CPUやメモリーの様に0、1が伝わればいいならば鈍っていて問題ないので簡単だが(といっても最近のようにGHz帯になると簡単ではないだろうが)、ジッターを問題にするとなると立ち上がり、立下りが急峻でないといけないので事態は深刻になる。

使用したレシーバーのクロックに対するジッター性能の仕様は0.2nsで上図の1目盛り(DIV)の1/80だ。本当にそれだけのジッター性能があったとしても波形がこれだけ鈍っていたらDACで受けたときにジッターは100倍くらい悪くなってもおかしくない。そもそもデジタル回路はトランジスタのON・OFFだけを取り扱うので、そのON・OFFをどの閾値で行うかは極めてあいまいなのだ。

何が言いたいかと言うと、マスタークロック周りで重要なのは発振部のジッターの小ささではなく、波形の質(立ち上がり、立ち下がり)、伝送経路の高周波領域の完全性という事だ 。言い換えればジッターを抑制するのにジッターの小さな発信器を使用しても必ずしも効果は期待できず、むしろ波形の質、ドライブ能力などに着目した方がジッターが抑えられるという事だ。

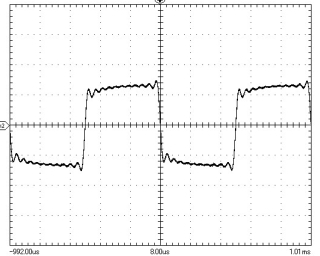

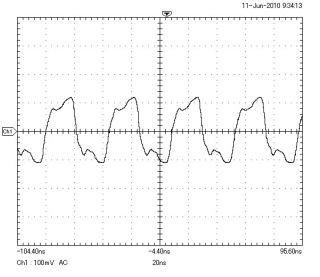

ついでにいただいたコメント(クイズの回答)に対しても解説しておく。乱れた矩形波信号ではないかという回答があったが、CDPの矩形波応答はこんな感じだ。

CDPで再生した1KHz矩形波信号波形

CDPで再生した1KHz矩形波信号波形

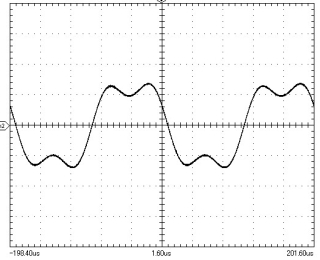

CDPで再生した5KHz矩形波信号波形

CDPで再生した5KHz矩形波信号波形

CDの場合、20KHz以上がスパッとなくなっているのでリンギングがある様に見えるがこれは正常で仕方が無い事なのだ。5KHzになると5KHzと3倍の15KHzの合成波になるから、もう正弦波丸出しという感じになる。

実を言うとこの波形はかなりいいほうで、実際にはCDPのアナログ周りはもっと悲惨な事になっている。その辺の事情は自社製DACを出す際に紹介するつもり。

【内容の修正とお詫び】

内容に測定上の誤りがありましたので修正させていただきます。コメントを頂き再度調べてみましたが、測定時に初歩的な間違いをしていました。

オシロのプローブを1:1(プローブの入力Z1MΩ、46pF)で測定していたのですが1:10(10MΩ、12pF)で再測定したら、システムクロックはこの様になりました。

11.3MHzのシステムクロック波形(この波形は48Khzfs入力時のシステムクロックです)

11.3MHzのシステムクロック波形(この波形は48Khzfs入力時のシステムクロックです)

プローブ:TEXAS製250MHzプローブ

オシロ:200MHz(5Gs/s)SDS200A

波形は綺麗とはいえませんが立ち上がりはそこそこ鋭くデジタル信号としては十分だと思います。10MHz帯になると10pFの容量でも数KΩの負荷になるので重たくなってしまうのです。1:10のプローブでも真の波形が取れているかは怪しいかもしれません。オーディオアンプなどですともともと駆動能力があるので、数pFの容量では影響を受けないのですがロジック系のICは負荷が軽い事を前提に作られているので、この辺はもっと気をつけて調べなくてはいけませんでした。お詫びと共に訂正させていただきます。 100MHzのアナログオシロだと上図の波形を少し丸くした感じなります。

ちなみに96Khzのサンプリング周波数に対するシステムクロック波形は次の通り。

22.6MHzのシステムクロック波形(この波形は96Khz fs入力時のシステムクロックです)

22.6MHzのシステムクロック波形(この波形は96Khz fs入力時のシステムクロックです)

かなり怪しい形だが何とかいけそうな感じです。

今後ともよろしくお願いいたします。

Kei

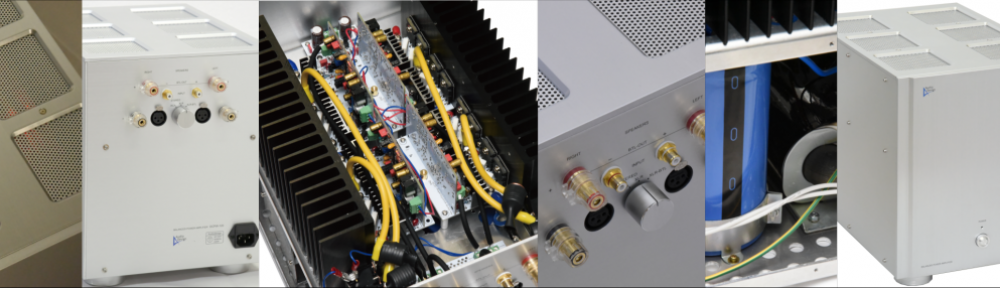

DAC