前回はDAC内のクロック信号について概略を紹介しましたが、今回はもう少し詳しく解説しましょう。

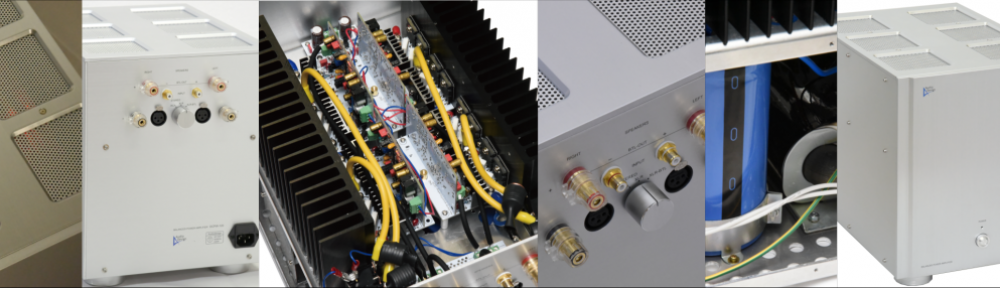

DAC内の構成はこうなっていました。

この中でレシーバーと呼ばれるチップがCDプレーヤーからのデジタル信号(サンプリング周波数44.1KHz)を受けてさまざまなクロック信号を発生させます。入力のサンプリング周波数44.1KHzのデジタル信号はシリアルデータで左右16bitのデータを含むために実際には64倍の2.8224MHzの周波数のデータになっています。結構高周波帯域に近いでしょう。

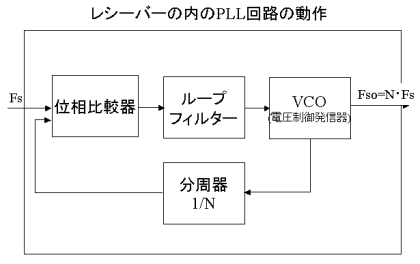

44.1KHzといっても実際には多少変動したり、最初からずれているので、受け取った44.1KHz(実際には2.8224MHz)あたりの周波数で、入力信号に正確に同期した整数倍の周波数のクロック信号を発生させる必要が有ります。このためにPLL(位相同期)回路というものを使用します。

PLL回路のブロック図は一般にこうなっています。

このブロックをみてもイメージがわかないと思います。なにしろPLL回路の理解だけで一冊の本が必要なので・・・。とにかく入力信号の整数倍の信号を発生する回路があって、CDPプレーヤーにしろ、DAC製品にしろ、レシーバーと呼ばれるチップが入っていてそのチップが100%PLL回路を使用しているということです(外部クロックは使用してないという事)。それでも実際に外部クロックが使用できるDAC製品もありますが、それはどういう動作をしているかはまたこの次に説明しましょう。